Page 25 - Міністерство освіти і науки України

P. 25

керування мікроЕОМ обчислює керуюче діяння u n, яке

перевіряється на обмеження за максимумом і мінімумом: u min

u n u max. Якщо ця умова виконується, то сигнал u n

передається ЦАП і далі ВМ.

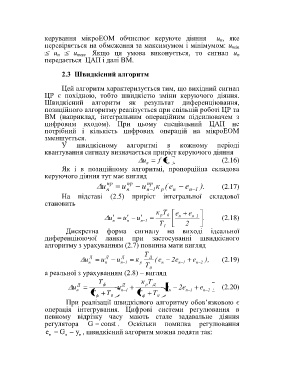

2.3 Швидкісний алгоритм

Цей алгоритм характеризується тим, що вихідний сигнал

ЦР є похідною, тобто швидкістю зміни керуючого діяння.

Швидкісний алгоритм як результат диференціювання,

позиційного алгоритму реалізується при спільній роботі ЦР та

ВМ (наприклад, інтегральним операційним підсилювачем з

цифровим входом). При цьому спеціальний ЦАП не

потрібний і кількість цифрових операцій на мікроЕОМ

зменшується.

У швидкісному алгоритмі в кожному періоді

квантування сигналу визначається приріст керуючого діяння

u n f e n . (2.16)

Як і в позиційному алгоритмі, пропорційна складова

керуючого діяння тут має вигляд

u пр u n пр u n пр 1 к р е ( n e n 1 ). (2.17)

n

На підставі (2.5) приріст інтегральної складової

становить

к р Т 0 e e

u n u n u n 1 n n 1 . (2.18)

Т І 2

Дискретна форма сигналу на виході ідеальної

диференціюючої ланки при застосуванні швидкісного

алгоритму з урахуванням (2.7) повинна мати вигляд

Т

u Д u Д u Д к Д е ( e 2 e ), (2.19)

1

n

n

n

р

Т 0 n n 1 n 2

а реальної з урахуванням (2.8) – вигляд

Т к Т

u n Д ф u n Д 1 р Д e n e 2 n 1 e n 2 . (2.20)

Т ф Т 0 Т ф Т 0

При реалізації швидкісного алгоритму обов’язковою є

операція інтегрування. Цифрові системи регулювання в

певному відрізку часу мають стале задавальне діяння

регулятора G const . Оскільки помилка регулювання

e n G n y , швидкісний алгоритм можна подати так:

n