Page 27 - 6733

P. 27

D0 Y0

D1 MUX DMX Y1

D2 Y2

D3

Дані D4 D Y3

Y4

D5

D6 Y Y5

Y6

D7 Y7

Адреси A0 A0

A1

A1

A2

A2

EO EO

а) б)

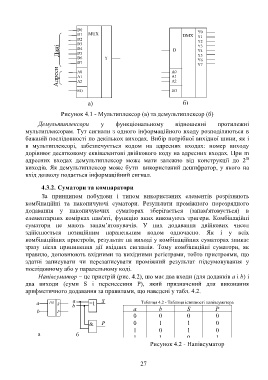

Рисунок 4.1 - Мультиплексор (а) та демультиплексор (б)

Демультиплексори у функціональному відношенні протилежні

мультиплексорам. Тут сигнали з одного інформаційного входу розподіляються в

бажаній послідовності по декількох виходах. Вибір потрібної вихідної шини, як і

в мультиплексорі, забезпечується кодом на адресних входах: номер виходу

дорівнює десятковому еквівалентові двійкового коду на адресних входах. При m

m

адресних входах демультиплексор може мати залежно від конструкції до 2

виходів. Як демультиплексор може бути використаний дешифратор, у якого на

вхід дозволу подається інформаційний сигнал.

4.3.2. Суматори та компаратори

За принципом побудови і типом використаних елементів розрізняють

комбінаційні та накопичуючі суматори. Результати проміжного порозрядного

додавання у накопичуючих суматорах зберігається (запам'ятовується) в

елементарних комірках пам'яті, функцію яких викоиують тригери. Комбінаційні

суматори не мають запам’ятовувачів. У них додавання двійкових чисел

здійснюється позиційним паралельним кодом одночасно. Як і у всіх

комбінаційних пристроїв, результат на виході у комбінаційних суматорах зникає

зразу після припинення дії вхідних сигналів. Тому комбінаційні суматори, як

правило, доповнюють вхідними та вихідними регістрами, тобто пристроями, що

здатні записувати чи перезаписувати проміжний результат підсумовування у

послідовному або у паралельному коді.

Напівсуматор це пристрій (рис. 4.2), шо має два входи (для доданків a і b) і

два виходи (суми S і перенесення P), який призначений для виконання

арифметичного додавання за правилами, що наведені у табл. 4.2.

а HS S a =1 S Таблиця 4.2 - Таблиця істинності напівсуматора

b

b P a b S P

0 0 0 0

& P 0 1 1 0

1 0 1 0

a б

1 1 0 1

Рисунок 4.2 - Напівсуматор

27