Page 23 - 6733

P. 23

X0

X1 &

1

X2 &

&

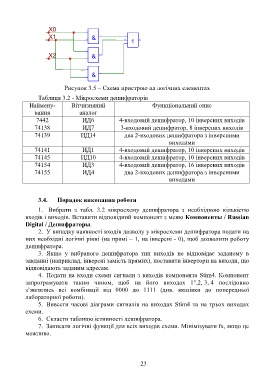

Рисунок 3.5 – Схема пристрою на логічних елементах

Таблиця 3.2 - Мікросхеми дешифраторів

Наймену- Вітчизняний Функціональний опис

вання аналог

7442 ИД6 4-входовий дешифратор, 10 інверсних виходів

74138 ИД7 3-входовий дешифратор, 8 інверсних виходів

74139 ИД14 два 2-входових дешифратора з інверсними

виходами

74141 ИД1 4-входовий дешифратор, 10 інверсних виходів

74145 ИД10 4-входовий дешифратор, 10 інверсних виходів

74154 ИД3 4-входовий дешифратор, 16 інверсних виходів

74155 ИД4 два 2-входових дешифратора з інверсними

виходами

3.4. Порядок виконання роботи

1. Вибрати з табл. 3.2 мікросхему дешифратора з необхідною кількістю

входів і виходів. Вставити відповідний компонент з меню Компоненты / Russian

Digital / Дешифраторы.

2. У випадку наявності входів дозволу у мікросхеми дешифратора подати на

них необхідні логічні рівні (на прямі – 1, на інверсні - 0), щоб дозволити роботу

дешифратора.

3. Якщо у вибраного дешифратора тип виходів не відповідає заданому в

завданні (наприклад, інверсні замість прямих), поставити інвертори на виходи, що

відповідають заданим адресам.

4. Подати на входи схеми сигнали з виходів компонента Stim4. Компонент

запрограмувати таким чином, щоб на його виходах 1°,2, 3, 4 послідовно

з’являлись всі комбінації від 0000 до 1111 (див. вказівки до попередньої

лабораторної роботи).

5. Вивести часові діаграми сигналів на виходах Stim4 та на трьох виходах

схеми.

6. Скласти таблицю істинності дешифратора.

7. Записати логічні функції для всіх виходів схеми. Мінімізувати їх, якщо це

можливо.

23