Page 32 - 6733

P. 32

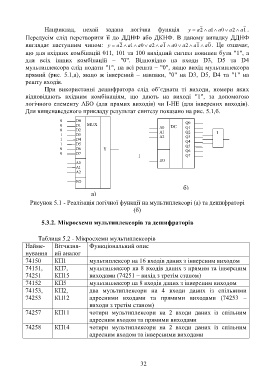

Наприклад, нехай задана логічна функція y a 2 a 1 a 0 a 2 a 1 .

Передусім слід перетворити її до ДДНФ або ДКНФ. В даному випадку ДДНФ

виглядає наступним чином: y a 2 a 1 a 0 a 2 a 1 a 0 a 2 a 1 a 0. Це означає,

що для вхідних комбінацій 011, 101 та 100 вихідний сигнал повинен бути "1", а

для всіх інших комбінацій – "0". Відповідно на входи D3, D5 та D4

мультиплексора слід подати "1", на всі решта – "0", якщо вихід мультиплексора

прямий (рис. 5.1,а), якщо ж інверсний – навпаки, "0" на D3, D5, D4 та "1" на

решту входів.

При використанні дешифратора слід об’єднати ті виходи, номери яких

відповідають вхідним комбінаціям, що дають на виході "1", за допомогою

логічного елементу АБО (для прямих виходів) чи І-НЕ (для інверсних виходів).

Для вищенаведеного прикладу результат синтезу показано на рис. 5.1,б.

0 D0 Q0

0 D1 MUX A0 DС Q1

0 D2 A1 Q2

1 D3 A2 Q3 1

1 D4 Q4

1 D5 Q5

0 D6 Y Q6

0 D7 Q7

1 EO

A0

A1

A2

EO

б)

а)

Рисунок 5.1 - Реалізація логічної функції на мультиплексорі (а) та дешифраторі

(б)

5.3.2. Мікросхеми мультиплексорів та дешифраторів

Таблиця 5.2 - Мікросхеми мультиплексорів

Найме- Вітчизня- Функціональний опис

нування ий аналог

74150 КП1 мультиплексор на 16 входів даних з інверсним виходом

74151, КП7, мультиплексор на 8 входів даних з прямим та інверсним

74251 КП15 виходами (74251 – вихід з третім станом)

74152 КП5 мультиплексор на 8 входів даних з інверсним виходом

74153, КП2, два мультиплексори на 4 входи даних із спільними

74253 КП12 адресними входами та прямими виходами (74253 –

виходи з третім станом)

74257 КП11 чотири мультиплексори на 2 входи даних із спільним

адресним входом та прямими виходами

74258 КП14 чотири мультиплексори на 2 входи даних із спільним

адресним входом та інверсними виходами

32