Page 37 - 6733

P. 37

активному рівні синхросигнала С інформація з входів безперешкодно проходить

на виходи. Часові діаграми приведені на рис .6.4.

До моменту часу t4 сигнал С = 1 і вихідне значення визначається

комбінаціями сигналів R і S. Протягом інтервалу часу t0...t1 на вході R діє 1, а

сигнал S=0, тому на виході Q також 0. Починаючи з моменту t1 і до моменту t2

R=S=0 і діє режим пам'яті (Q не змінюється). У момент t2 R=0, а S=1 і трігер

встановлюється (Q=1). З моменту закінчення імпульсу S і до моменту t3 трігер

зберігає цю одиницю, а у момент t3 скидається, оскільки R=0, а S=1. Аналогічно

можна проаналізувати і решту станів виходу.

6.3.3. D-трігери

D-трігер має два входи: інформаційний вхід D(аtа) і вхід управління

записом/запам'ятовуванням L(oad) /L(atch) - звідси його друга назва: "защіпка".

Останній вхід часто позначають символом С(lock). Вихідний сигнал Q приймає

значення, рівне вхідному D, при C = 1 і зберігає попереднє значення Q(t+dt)= Q(t)

при C = 0.

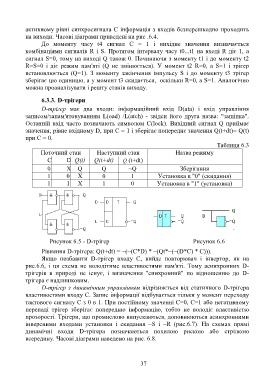

Таблиця 6.3

Поточний стан Наступний стан Назва режиму

С D Q(t) Q(t+dt) Q (t+dt)

0 X Q Q ~Q Зберігання

1 0 X 0 1 Установка в "0" (скидання)

1 1 X 1 0 Установка в "1" (установка)

Рисунок 6.5 - D-трігер Рисунок 6.6

Рівняння D-трігера: Q(t+dt) = ~(~(C*D) * ~(Qt*~(~(D*C) * C))).

Якщо позбавити D-трігер входу С, вийде повторювач і інвертор, як на

рис.6.6, і ця схема не володітиме властивостями пам'яті. Тому асинхронних D-

трігерів в природі не існує, і визначення "синхронний" по відношенню до D-

трігера є надлишковим.

D-трігер з динамічним управлінням відрізняється від статичного D-трігера

властивостями входу С. Запис інформації відбувається тільки у момент переходу

тактового сигналу С з 0 в 1. При постійному значенні С=0, С=1 або негативному

перепаді трігер зберігає попередню інформацію, тобто не володіє властивістю

прозорості. Трігери, що промислово випускаються, доповнюються асинхронними

інверсними входами установки і скидання ~S і ~R (рис.6.7). На схемах прямі

динамічні входи D-трігера позначаються похилою рискою або стрілкою

всередину. Часові діаграми наведено на рис. 6.8.

37