Page 124 - 6111

P. 124

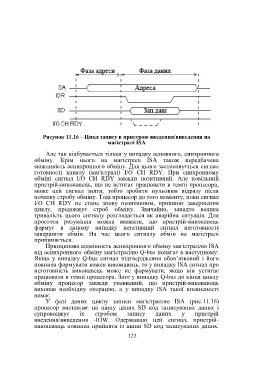

Рисунок 11.16 – Цикл запису в пристрою введення/виведення на

магістралі ISA

Але так відбувається тільки у випадку основного, синхронного

обміну. Крім нього на магістралі ISA також передбачена

можливість асинхронного обміну. Для цього застосовується сигнал

готовності каналу (магістралі) I/O CH RDY. При синхронному

обміні сигнал I/O CH RDY завжди позитивний. Але повільний

пристрій-виконавець, що не встигає працювати в темпі процесора,

може цей сигнал зняти, тобто зробити нульовим відразу після

початку стробу обміну. Тоді процесор до того моменту, поки сигнал

I/O CH RDY не стане знову позитивним, припиняє завершення

циклу, продовжує строб обміну. Звичайно, занадто велика

тривалість цього сигналу розглядається як аварійна ситуація. Для

простоти розуміння можна вважати, що пристрій-виконавець

формує в даному випадку негативний сигнал неготовності

завершити обмін. На час цього сигналу обмін на магістралі

припиняється.

Принципова відмінність асинхронного обміну магістраллю ISA

від асинхронного обміну магістраллю Q-bus полягає в наступному:

Якщо у випадку Q-bus сигнал підтвердження обов’язковий і його

повинен формувати кожен виконавець, то у випадку ISA сигнал про

неготовність виконавець може не формувати, якщо він устигає

працювати в темпі процесора. Зате у випадку Q-bus до кінця циклу

обміну процесор завжди упевнений, що пристрій-виконавець

виконав необхідну операцію, а у випадку ISA такої впевненості

немає.

У фазі даних циклу записи магістраллю ISA (рис.11.16)

процесор виставляє на шину даних SD код записуваних даних і

супроводжує їх стробом запису даних у пристрій

введення/виведення -IOW. Одержавши цей сигнал, пристрій-

виконавець повинен прийняти із шини SD код записуваних даних.

123