Page 123 - 6111

P. 123

кожен з циклів читання чи запису, але менше часу, ніж два

послідовно виконаних цикли читання і запису (тому що для нього

потрібна тільки одна адресна фаза). Сигнал -SYNC виробляється

процесором на початку циклу "ввід-пауза-вивід" і тримається до

закінчення всього циклу.

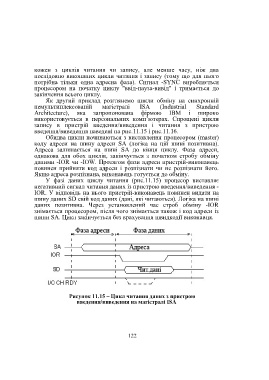

Як другий приклад розглянемо цикли обміну на синхронній

немультиплексованій магістралі ISA (Industrial Standard

Architecture), яка запропонована фірмою IBM і широко

використовується в персональних комп’ютерах. Спрощені цикли

запису в пристрій введення/виведення і читання з пристрою

введення/виведення наведені на рис.11.15 і рис.11.16.

Обидва цикли починаються з виставлення процесором (master)

коду адреси на шину адреси SA (логіка на цій шині позитивна).

Адреса залишається на шині SA до кінця циклу. Фаза адреси,

однакова для обох циклів, закінчується з початком стробу обміну

даними -IOR чи -IOW. Протягом фази адреси пристрій-виконавець

повинен прийняти код адреси і розпізнати чи не розпізнати його.

Якщо адреса розпізнана, виконавець готується до обміну.

У фазі даних циклу читання (рис.11.15) процесор виставляє

негативний сигнал читання даних із пристрою введення/виведення -

IOR. У відповідь на нього пристрій-виконавець повинен видати на

шину даних SD свій код даних (дані, які читаються). Логіка на шині

даних позитивна. Через установлений час строб обміну -IOR

знімається процесором, після чого знімається також і код адреси із

шини SA. Цикл закінчується без врахування швидкодії виконавця.

Рисунок 11.15 – Цикл читання даних з пристрою

введення/виведення на магістралі ISA

122