Page 129 - 6111

P. 129

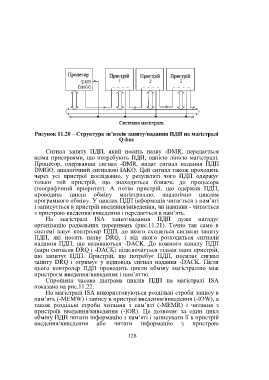

Рисунок 11.20 – Структура зв’язків запиту/надання ПДП на магістралі

Q-bus

Сигнал запиту ПДП, який носить назву -DMR, передається

всіма пристроями, що потребують ПДП, однією лінією магістралі.

Процесор, одержавши сигнал -DMR, видає сигнал надання ПДП

DMGO, аналогічний сигналові IAKO. Цей сигнал також проходить

через усі пристрої послідовно, у результаті чого ПДП одержує

тільки той пристрій, що знаходиться ближче до процесора

(географічний пріоритет). А потім пристрій, що одержав ПДП,

проводить цикли обміну магістраллю, аналогічно циклам

програмного обміну. У циклах ПДП інформація читається з пам’яті

і записується в пристрій введення/виведення, чи навпаки - читається

з пристрою введення/виведення і передається в пам’ять.

На магістралі ISA запит/надання ПДП дуже нагадує

організацію радіальних переривань (рис.11.21). Точно так само в

системі існує контролер ПДП, до якого сходяться сигнали запиту

ПДП, які носять назву DRQ, і від якого розходяться сигнали

надання ПДП, що називаються -DACK. До кожного каналу ПДП

(пари сигналів DRQ і -DACK) підключається тільки один пристрій,

що запитує ПДП. Пристрій, що потребує ПДП, посилає сигнал

запиту DRQ і отримує у відповідь сигнал надання -DACK. Після

цього контролер ПДП проводить цикли обміну магістраллю між

пристроєм введення/виведення і пам’яттю.

Спрощена часова діаграма циклів ПДП на магістралі ISA

показана на рис.11.22.

На магістралі ISA використовуються роздільні строби запису в

пам’ять (-MEMW) і запису в пристрої введення/виведення (-IOW), а

також роздільні строби читання з пам’яті (-MEMR) і читання з

пристроїв введення/виведення (-IOR). Це дозволяє за один цикл

обміну ПДП читати інформацію з пам’яті і записувати її в пристрій

введення/виведення або читати інформацію з пристрою

128