Page 121 - 6111

P. 121

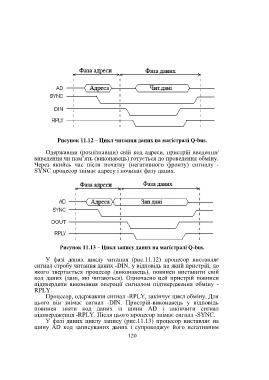

Рисунок 11.12 – Цикл читання даних на магістралі Q-bus.

Одержавши (розпізнавши) свій код адреси, пристрій введення/

виведення чи пам’ять (виконавець) готується до проведення обміну.

Через якийсь час після початку (негативного фронту) сигналу -

SYNC процесор знімає адресу і починає фазу даних.

Рисунок 11.13 – Цикл запису даних на магістралі Q-bus.

У фазі даних циклу читання (рис.11.12) процесор виставляє

сигнал стробу читання даних -DIN, у відповідь на який пристрій, до

якого звертається процесор (виконавець), повинен виставити свій

код даних (дані, які читаються). Одночасно цей пристрій повинен

підтвердити виконання операції сигналом підтвердження обміну -

RPLY.

Процесор, одержавши сигнал -RPLY, закінчує цикл обміну. Для

цього він знімає сигнал -DIN. Пристрій-виконавець у відповідь

повинен зняти код даних із шини AD і закінчити сигнал

підтвердження -RPLY. Після цього процесор знімає сигнал -SYNC.

У фазі даних циклу запису (рис.11.13) процесор виставляє на

шину AD код записуваних даних і супроводжує його негативним

120