Page 207 - 6111

P. 207

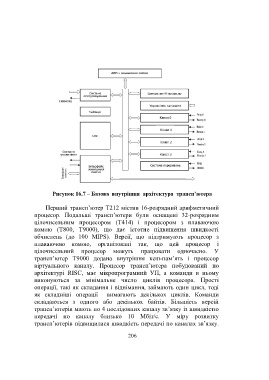

Рисунок 16.7 – Базова внутрішня архітектура трансп’ютера

Перший трансп’ютер Т212 містив 16-розрядний арифметичний

процесор. Подальші трансп’ютери були оснащені 32-розрядним

цілочисельним процесором (Т414) і процесором з плаваючою

комою (Т800, Т9000), що дає істотне підвищення швидкості

обчислень (до 100 MIPS). Версії, що підтримують процесор з

плаваючою комою, організовані так, що цей процесор і

цілочисельний процесор можуть працювати одночасно. У

трансп’ютер Т9000 додана внутрішня кеш-пам’ять і процесор

віртуального каналу. Процесор трансп’ютера побудований по

архітектурі RISC, має мікропрограмний УП, а команди в ньому

виконуються за мінімальне число циклів процесора. Прості

операції, такі як складання і віднімання, займають один цикл, тоді

як складніші операції вимагають декількох циклів. Команди

складаються з одного або декількох байтів. Більшість версій

трансп’ютерів мають по 4 послідовних каналу зв’язку із швидкістю

передачі по каналу близько 10 Мбіт/с. У міру розвитку

трансп’ютерів підвищилася швидкість передачі по каналах зв’язку.

206