Page 58 - 4863

P. 58

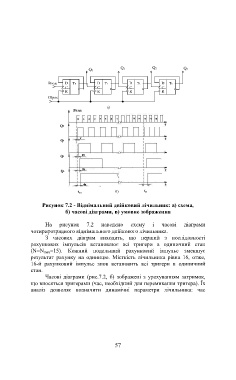

Q 1 Q2 Q3

Q 0

Вход D T0 D T1 D T2 D T3

C C C C

R R R R

Сброс

a)

Вход

Q 0

Q 1

Q 2

Q 3

б)

t сл t р

Рисунок 7.2 - Віднімальний двійковий лічильник: а) схема,

б) часові діаграми, в) умовне зображення

На рисунок 7.2 наведено схему і часові діаграми

чотирирозрядного віднімального двійкового лічильника.

З часових діаграм виходить, що перший з послідовності

рахункових імпульсів встановлює всі тригери в одиничний стан

(N=N max=15). Кожний подальший рахунковий імпульс зменшує

результат рахунку на одиницю. Місткість лічильника рівна 16, отже,

16-й рахунковий імпульс знов встановить всі тригери в одиничний

стан.

Часові діаграми (рис.7.2, б) зображені з урахуванням затримок,

що вносяться тригерами (час, необхідний для перемикання тригера). Їх

аналіз дозволяє визначити динамічні параметри лічильника: час

57