Page 20 - 4833

P. 20

Сигнал на вході К вимикає тригер за зрізом тактового імпульсу С.

За наявністю сигналів J = K = 0 надходження тактових імпульсів не

викликає змін у стані тригера. Якщо ж вхідні сигнали J = K = 1,

надходження тактового імпульсу перекидає тригер до протилежного

стану: Q n+1 = Q (для RS-тригерів така вхідна комбінація сигналів

n

заборонена).

Промисловість випускає готові JK-тригери у вигляді

інтегральних мікросхем (ІМС), які мають додаткові установчі входи

R і S. Ці входи асинхронні. Після подачі R = 0, S = 1 тригер миттєво

встановлює на виході Q n+1 = 1, а після подачі сигналів R = 1, S = 0

встановлює Q n+1 = 0. Таблиця істинності JK-тригера наведена в

таблиці 2.3.

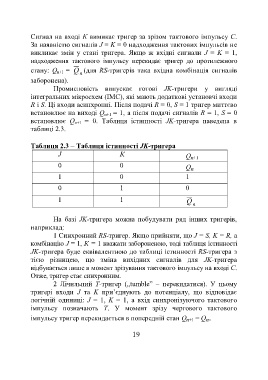

Таблиця 2.3 – Таблиця істинності JK-тригера

J К Q n+1

0 0 Q n

1 0 1

0 1 0

1 1 Q

n

На базі JK-тригера можна побудувати ряд інших тригерів,

наприклад:

1 Синхронний RS-тригер. Якщо прийняти, що J = S, K = R, a

комбінацію J = 1, К = 1 вважати забороненою, тоді таблиця істинності

JK-тригера буде еквівалентною до таблиці істинності RS-тригера з

тією різницею, що зміна вихідних сигналів для JK-тригера

відбувається лише в момент зрізування тактового імпульсу на вході С.

Отже, тригер стає синхронним.

2 Лічильний Т-тригер („tumble” – перекидатися). У цьому

тригері входи J та K при’єднують до потенціалу, що відповідає

логічній одиниці: J = 1, K = 1, а вхід синхронізуючого тактового

імпульсу позначають Т. У момент зрізу чергового тактового

імпульсу тригер перекидається в попередній стан Q n+1 = Q n.

19