Page 24 - 4833

P. 24

ЛАБОРАТОРНА РОБОТА № 3

ДОСЛІДЖЕННЯ ПАРАЛЕЛЬНОГО, ПОСЛІДОВНОГО ТА

УНІВЕРСАЛЬНОГО РЕГІСТРІВ

Мета роботи

Вивчити будову і принцип дії чотирирозрядних

паралельних, послідовних та універсальних регістрів.

1 Основні теоретичні відомості

Регістри – це функціональні пристрої, призначені для запису,

зберігання та видачі інформації у вигляді двійкових кодів. Для

зберігання кожного двійкового розряду в регістрі використовують

одну тригерну комірку. Отже, для зберігання п - розрядного двійкового

коду регістр повинен мати п - кількість тригерів.

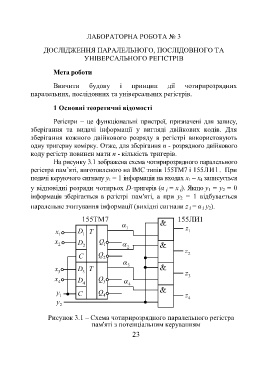

На рисунку 3.1 зображена схема чотирирозрядного паралельного

регістра пам’яті, виготовленого на ІМС типів 155ТМ7 і 155ЛИ1. При

подачі керуючого сигналу у 1 = 1 інформація на входах х 1 – х 4 записується

у відповідні розряди чотирьох D-тригерів (α і = х і ). Якщо у 1 = у 2 = 0

інформація зберігається в регістрі пам'яті, а при у 2 = 1 відбувається

паралельне зчитування інформації (вихідні сигнали z і = α і у 2).

155 TM 7 155 ЛИ1

1

x D T z 1

1 1

x D Q

2 2 1

2 z

C Q 2 2

3

x D T

3 3 z

x Q 3

4 D 4 3 4

y C Q

1 4 z 4

y

2

Рисунок 3.1 – Схема чотирирозрядного паралельного регістра

пам'яті з потенціальним керуванням

23