Page 25 - 4833

P. 25

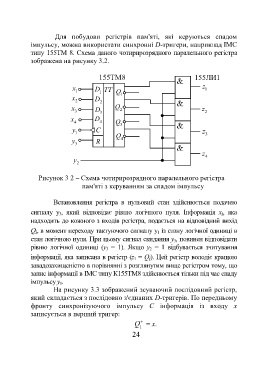

Для побудови регістрів пам'яті, які керуються спадом

імпульсу, можна використати синхронні D-тригери, наприклад ІМС

типу 155ТМ 8. Схема даного чотирирозрядного паралельного регістра

зображена на рисунку 3.2.

155 TM 8 155 ЛИ1

x D TT z 1

1 1 Q 1

x D

2 2

x D Q 2 z

3 3 2

x D

4 4 Q

3

y C z

1 3

Q 4

y R

3

z 4

y

2

Рисунок 3 2 – Схема чотирирозрядного паралельного регістра

пам'яті з керуванням за спадом імпульсу

Встановлення регістра в нульовий стан здійснюється подачею

сигналу у 3, який відповідає рівню логічного нуля. Інформація х і , яка

надходить до кожного з входів регістра, подається на відповідний вихід

Q і , в момент переходу тактуючого сигналу у 1 із стану логічної одиниці в

стан логічною нуля. При цьому сигнал скидання у 3, повинен відповідати

рівню логічної одиниці (у 3 = 1). Якщо у 2 = 1 відбувається зчитування

інформації, яка записана в регістр (z 1 = Q і ). Цей регістр володіє кращою

завадозахищеністю в порівнянні з розглянутим вище регістром тому, що

запис інформації в ІМС типу К155ТМ8 здійснюється тільки під час спаду

імпульсу у 1.

На рисунку 3.3 зображений зсуваючий послідовний регістр,

який складається з послідовно з'єднаних D-тригерів. По передньому

фронту синхронізуючого імпульсу С інформація із входу х

записується в перший тригер:

Q = x.

1

24