Page 17 - 4833

P. 17

S I S

S Q t

S T Q

R

t

R Q Q Q

R

а) R II

б) Q t

в)

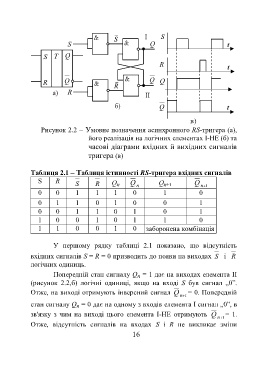

Рисунок 2.2 – Умовне позначення асинхронного RS-тригера (а),

його реалізація на логічних елементах І-НЕ (б) та

часові діаграми вхідних й вихідних сигналів

тригера (в)

Таблиця 2.1 – Таблиця істинності RS-тригера вхідних сигналів

S R S R Q n Q Q n+1 Q n 1

n

0 0 1 1 1 0 1 0

0 1 1 0 1 0 0 1

0 0 1 1 0 1 0 1

1 0 0 1 0 1 1 0

1 1 0 0 1 0 заборонена комбінація

У першому рядку таблиці 2.1 показано, що відсутність

вхідних сигналів S = R = 0 призводить до появи на виходах S і R

логічних одиниць.

Попередній стан сигналу Q n = 1 дає на виходах елемента ІІ

(рисунок 2.2,б) логічні одиниці, якщо на вході S був сигнал „0”.

Отже, на виході отримують інверсний сигнал Q = 0. Попередній

n 1

стан сигналу Q n = 0 дає на одному з входів елемента І сигнал „0”, в

зв'язку з чим на виході цього елемента І-НЕ отримують Q = 1.

n 1

Отже, відсутність сигналів на входах S і R не викликає зміни

16