Page 38 - 4143

P. 38

o масив локальної пам'яті вагових коефіцієнтів (Sunaptic

RAM); час доступу до пам'яті з боку зовнішніх пристроїв (за

адресною мультиплексною шиною трансп'ютера) складає

150 нс;

o два блоки регістрів станів нейрону (Neural State Register

(NSR)); у кожному блоці міститься 16 універсальних

байтових регістрів, що забезпечують зберігання і

модифікацію в синхронному і асинхронному режимах

значень виходів нейронів;

o блок процесорів і регістрів навчання (Learning Register), що

містить 16 регістрів, кожний з яких забезпечує зберігання, а

також виконання операцій складання і віднімання 16-бітових

операндів, що є значеннями вагових коефіцієнтів.

o блок помножувачів, що складається з 16 схем множення

байтового операнда на біт (AND); за допомогою даного

блоку обчислюються елементарні твори для знаходження

зваженої суми;

o блок накопичувального суматора, що забезпечує складання

приватних сум і накопичення результату в

накопичувальному регістрі у разі обчислення вихідного

значення нейрона, що має більше 16 входів або значення

виходу більше 1 біта;

o блок дешифрации команд і мікропрограмного управління,

що забезпечує виконання 19-розрядних команд і

мікропрограм.

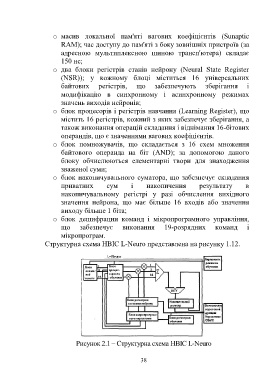

Структурна схема НВІС L-Neuro представлена на рисунку 1.12.

Рисунок 2.1 – Структурна схема НВІС L-Neuro

38