Page 112 - 149

P. 112

вбудовані у ВІС МП і призначені для зберігання команд, операндів і

результатів проміжних перетворень. Розрядність регістрів відповідає

розрядності МП, а їх загальна кількість обмежена розмірами кристала.

Надоперативні ОЗП виконані за єдиною з логічним елементом технологією і є

набором регістрів на статичних тригерах, які не вимагають регенерації

інформації, що в них зберігається . В мікропроцесорах великої продуктив-

ності , які є основою сучасних ПЕОМ , застосовується кеш-пам’ять ,що є

різновидом надоперативної пам’яті.Вона є буфером між ОЗП і його

“клієнтами”- процесором(одним або декількома )та іншими абонентами

системної шини. Кеш-пам’ять не являється самостійним сховищем :

інформація в ній не адресується клієнтами підсистеми пам’яті , присутність

кеша для них є “ прозорою”.Кеш зберігає копії блоків даних тих областей ОЗП

до яких були останні звернення і можливе повторне звернення до них буде

обслужене кеш-пам’яттю значно швидше ніж ОЗП. Кеш в сучасних

комп’ютерах збудований за дворівневою схемою :

■ Первинний кеш або L1 Cache –кеш 1 рівня,внутрішній кеш процесора

класа 486 і старших для програмних кодів та даних.

■ Вторинний кеш або L2 Cache- кеш 2 рівня . Інколи це зовнішній кеш ,

що установлюється на системну плату , а в Pentium Pro , Pentium II та Pentium

III кеш розміщений в одному корпусі з процесором.

Існує велика кількість елементів ОЗП, але більшість з них має

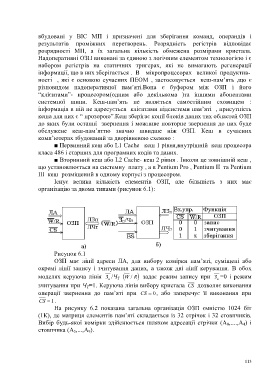

організацію за двома типами (рисунок 6.1):

Рисунок 6.1

ОЗП має лінії адреси ЛА, для вибору комірки пам’яті, суміщені або

окремі лінії запису і зчитування даних, а також дві лінії керування. В обох

моделях керуюча лінія З /Ч Т W R/ задає режим запису при З =0 і режим

п п

зчитування при Ч Т=1. Керуюча лінія вибору кристала CS дозволяє виконання

операції звернення до пам’яті при CS 0, або заперечує її виконання при

CS 1.

На рисунку 6.2 показана загальна організація ОЗП ємністю 1024 біт

(1К), де матриця елементів пам’яті складається із 32 стрічок і 32 стовпчиків.

Вибір будь-якої комірки здійснюється шляхом адресації стрічки (А 0,....,А 4) і

стовпчика (А 5,...,А 9).

113