Page 106 - 149

P. 106

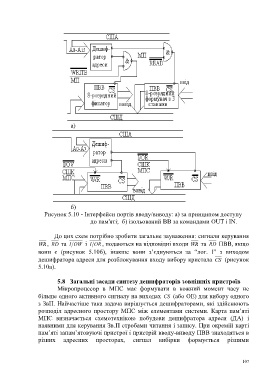

а)

б)

Рисунок 5.10 - Інтерфейси портів вводу/виводу: а) за принципом доступу

до пам'яті; б) ізольований ВВ за командами OUT і IN.

До цих схем потрібно зробити загальне зауваження: сигнали керування

WR, RD та I OW i I OR , подаються на відповідні входи WR та RD ПВВ, якщо

вони є (рисунок 5.10б), інакше вони з’єднуються за “лог. І” з виходом

дешифратора адреси для розблокування входу вибору кристала CS (рисунок

5.10а).

5.8 Загальні засади синтезу дешифраторів зовнішніх пристроїв

Мікропроцесор в МПС має формувати в кожний момент часу не

більше одного активного сигналу на виходах СS (або ОЕ) для вибору одного

з ЗвП. Найчастіше така задача вирішується дешифраторами, які здійснюють

розподіл адресного простору МПС між елементами системи. Карта пам’яті

МПС визначається схемотехнікою побудови дешифратора адреси (ДА) і

наявними для керування Зв.П стробами читання і запису. При окремій карті

пам’яті запам’ятовуючі пристрої і пристрій вводу-виводу ПВВ знаходяться в

різних адресних просторах, сигнал вибірки формується різними

107