Page 102 - 149

P. 102

5.5 Інтерфейс з ПЗП

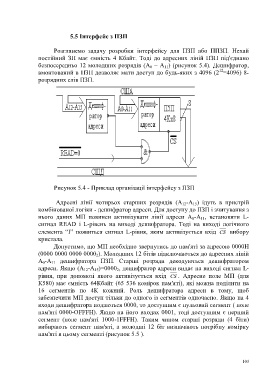

Розглянемо задачу розробки інтерфейсу для ПЗП або ППЗП. Нехай

постійний ЗП має ємність 4 Кбайт. Тоді до адресних ліній ПЗП під'єднано

безпосередньо 12 молодших розрядів (А 0 – А 11) (рисунок 5.4). Дешифратор,

12

вмонтований в ПЗП дозволяє мати доступ до будь-яких з 4096 (2 =4096) 8-

розрядних слів ПЗП.

Рисунок 5.4 - Приклад організації інтерфейсу з ПЗП

Адресні лінії чотирьох старших розрядів (А 12-А 15) ідуть в пристрій

комбінованої логіки - дешифратор адреси. Для доступу до ПЗП і зчитування з

нього даних МП повинен активізувати лінії адреси А 0-А 11, встановити L-

сигнал READ і L-рівень на виході дешифратора. Тоді на виході логічного

елемента “І” появиться сигнал L-рівня, яким активізується вхід CS вибору

кристала.

Допустимо, що МП необхідно звернутись до пам'яті за адресою 0000Н

(0000 0000 0000 0000 2). Молодших 12 бітів підключаються до адресних ліній

А 0-А 11 дешифратора ПЗП. Старші розряди декодуються дешифратором

адреси. Якщо (А 12-А 15)=0000 2, дешифратор адреси видає на виході сигнал L-

рівня, при допомозі якого активізується вхід CS . Адресне поле МП (для

К580) має ємність 64Кбайт (65 536 комірок пам'яті), які можна поділити на

16 сегментів по 4К кожний. Роль дешифратора адреси в тому, щоб

забезпечити МП доступ тільки до одного із сегментів одночасно. Якщо на 4

входи дешифратора подаються 0000, то доступним є нульовий сегмент ( поле

пам'яті 0000-ОFFFН). Якщо на його входах 0001, тоді доступним є перший

сегмент (поле пам'яті 1000-1FFFН). Таким чином старші розряди (4 біти)

вибирають сегмент пам'яті, а молодші 12 біт визначають потрібну комірку

пам'яті в цьому сегменті (рисунок 5.5 ).

103