Page 104 - 149

P. 104

Сигнал CS в схемі має низький рівень, коли сигнал вибірки адреси ОЗП

і сигнали READ або WRITE також L-рівня. Лінія WRITE з'єднана з входом W R

ОЗП, який має внутрішнє з'єднання за схемою “I” з другим входом CS .

Таким чином сигнал WRITE ігнорується до тих пір, доки CS Н-рівня.

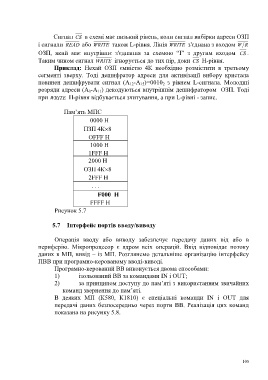

Приклад: Нехай ОЗП ємністю 4К необхідно розмістити в третьому

сегменті зверху. Тоді дешифратор адреси для активізації вибору кристала

повинен дешифрувати сигнал (А 12-А 15)=0010 2 з рівнем L-сигнала. Молодші

розряди адреси (А 0-А 11) декодуються внутрішнім дешифратором ОЗП. Тоді

при WRITE Н-рівня відбувається зчитування, а при L-рівні - запис.

Пам’ять МПС

0000 H

ПЗП 4К8

ОFFF H

1000 H

1FFF H

2000 H

ОЗП 4К8

2FFF H

. . .

F000 H

FFFF H

Рисунок 5.7

5.7 Інтерфейс портів вводу/виводу

Операція вводу або виводу забезпечує передачу даних від або в

периферію. Мікропроцесор є ядром всіх операцій. Ввід відповідає потоку

даних в МП, вивід – із МП. Розглянемо детальніше організацію інтерфейсу

ПВВ при програмно-керованому вводі-виводі.

Програмно-керований ВВ виконується двома способами:

1) ізольований ВВ за командами IN i OUT;

2) за принципом доступу до пам’яті з використанням звичайних

команд звернення до пам’яті.

В деяких МП (К580, К1810) є спеціальні команди IN i OUT для

передачі даних безпосередньо через порти ВВ. Pеалізація цих команд

показана на рисунку 5.8.

105