Page 150 - 6111

P. 150

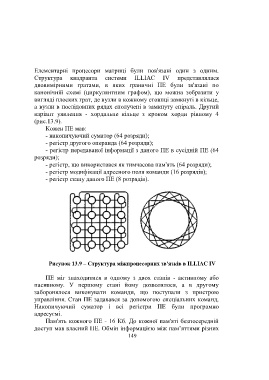

Елементарні процесори матриці були пов'язані один з одним.

Структура квадранта системи ILLIAC IV представлялася

двовимірними гратами, в яких граничні ПЕ були зв'язані по

канонічній схемі (циркулянтним графом), що можна зобразити у

вигляді плоских грат, де вузли в кожному стовпці замкнуті в кільце,

а вузли в послідовних рядах сполучені в замкнуту спіраль. Другий

варіант уявлення - хордальне кільце з кроком хорди рівному 4

(рис.13.9).

Кожен ПЕ мав:

- накопичуючий суматор (64 розряди);

- регістр другого операнда (64 розряди);

- регістр передаваної інформації з даного ПЕ в сусідній ПЕ (64

розряди);

- регістр, що використався як тимчасова пам'ять (64 розряди);

- регістр модифікації адресного поля команди (16 розрядів);

- регістр стану даного ПЕ (8 розрядів).

Рисунок 13.9 – Структура міжпроцесорних зв'язків в ILLIAC IV

ПЕ міг знаходитися в одному з двох станів - активному або

пасивному. У першому стані йому дозволялося, а в другому

заборонялося виконувати команди, що поступали з пристрою

управління. Стан ПЕ задавався за допомогою спеціальних команд.

Накопичуючий суматор і всі регістри ПЕ були програмно

адресуємі.

Пам'ять кожного ПЕ - 16 Кб. До кожної пам'яті безпосередній

доступ мав власний ПЕ. Обмін інформацією між пам’яттями різних

149