Page 144 - 6111

P. 144

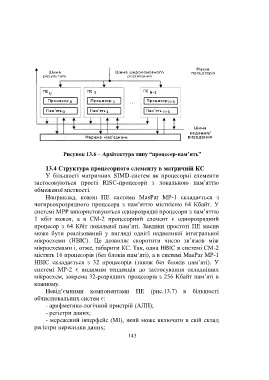

Рисунок 13.6 – Архітектура типу “процесор-пам’ять”

13.4 Структура процесорного елементу в матричній КС

У більшості матричних SIMD-систем як процесорні елементи

застосовуються прості RISC-процесори з локальною пам’яттю

обмеженої місткості.

Наприклад, кожен ПЕ системи MasPar MP-1 складається з

чотирьохрозрядного процесора з пам’яттю місткістю 64 Кбайт. У

системі МРР використовуються однорозрядні процесори з пам’яттю

1 кбіт кожен, а в СМ-2 процесорний елемент є однорозрядний

процесор з 64 Кбіт локальної пам’яті. Завдяки простоті ПЕ масив

може бути реалізований у вигляді однієї надвеликої інтегральної

мікросхеми (НВІС). Це дозволяє скоротити число зв’язків між

мікросхемами і, отже, габарити КС. Так, одна НВІС в системі СМ-2

містить 16 процесорів (без блоків пам’яті), а в системі MasPar MP-1

НВІС складається з 32 процесорів (також без блоків пам’яті). У

системі МР-2 є видимим тенденція до застосування складніших

мікросхем, зокрема 32-розрядних процесорів з 256 Кбайт пам’яті в

кожному.

Невід’ємними компонентами ПЕ (рис.13.7) в більшості

обчислювальних систем є:

- арифметико-логічний пристрій (АЛП);

- регістри даних;

- мережевий інтерфейс (МІ), який може включати в свій склад

регістри пересилки даних;

143