Page 113 - 6111

P. 113

У принципі, контролер ПДП може входити до складу пристрою

введення/виведення, якому потрібен режим ПДП або, навіть, до

складу декількох пристроїв введення/виведення.

Теоретично обмін за допомогою прямого доступу до пам’яті

може забезпечити більш високу швидкість передачі інформації,

аніж програмний обмін, тому що процесор передає дані повільніше,

ніж спеціалізований контролер ПДП. Однак на практиці ця перевага

реалізується далеко не завжди. Швидкість обміну в режимі ПДП

зазвичай обмежена можливостями магістралі. До того ж

необхідність програмного задавання режимів контролера ПДП

може звести нанівець виграш від більш високої швидкості

пересилання даних у режимі ПДП. Тому режим ПДП

застосовується рідко.

Якщо в системі вже існує самостійний контролер ПДП, то це

може в ряді випадків істотно спростити апаратуру пристроїв

введення/виведення, які працюють у режимі ПДП. У цьому, мабуть,

полягає єдина безперечна перевага режиму ПДП.

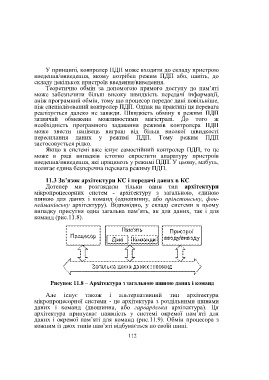

11.3 Зв’язок архітектури КС і передачі даних в КС

Дотепер ми розглядали тільки один тип архітектури

мікропроцесорних систем - архітектуру з загальною, єдиною

шиною для даних і команд (одношинну, або прінстонську, фон-

нейманівську архітектуру). Відповідно, у складі системи в цьому

випадку присутня одна загальна пам’ять, як для даних, так і для

команд (рис.11.8).

Рисунок 11.8 – Архітектура з загальною шиною даних і команд

Але існує також і альтернативний тип архітектури

мікропроцесорної системи - це архітектура з роздільними шинами

даних і команд (двошинна, або гарвардська архітектура). Ця

архітектура припускає наявність у системі окремої пам’яті для

даних і окремої пам’яті для команд (рис.11.9). Обмін процесора з

кожним із двох типів пам’яті відбувається по своїй шині.

112