Page 49 - 4863

P. 49

Q 3=a3

C Q 2=a2 Q 1 =a 1 Q 0=a0

C T3 C T2 C T1 C T0

D D D D

R R R R

Уст. “0”

Q 3 Q Q 1 Q 0

a 3 a0 2 a0

a2 a1

a) С RG D0

DI

0 0

1 1

2 2

3 3

R

б)

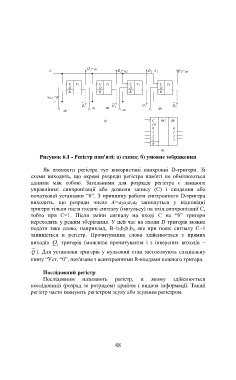

Рисунок 6.1 - Регістр пам'яті: а) схема; б) умовне зображення

Як елементи регістра тут використані синхронні D-тригери. Зі

схеми виходить, що окремі розряди регістра пам'яті не обмінюються

даними між собою. Загальними для розрядів регістра є ланцюги

управління: синхронізації або дозволи запису (С) і скидання або

початкової установки “0”. З принципу роботи синхронного D-тригера

виходить, що розряди числа А=а 3а 2а 1а 0 запишуться у відповідні

тригери тільки після подачі сигналу (імпульсу) на вхід синхронізації С,

тобто при С=1. Після зміни сигналу на вході С на “0” тригери

переходять у режим зберігання. У цей час на входи D тригерів можна

подати таке слово, наприклад, В=b 3b 2b 1b 0, яке при появі сигналу С=1

запишеться в регістр. Прочитування слова здійснюється з прямих

виходів Q тригерів (можливе прочитування і з інверсних виходів –

i

Q ). Для установки тригерів у нульовий стан застосовують спеціальну

шину “Уст. “0”, пов'язана з асинхронними R-входами кожного тригера.

Послідовний регістр

Послідовним називають регістр, в якому здійснюється

послідовний (розряд за розрядом) прийом і видача інформації. Такий

регістр часто іменують регістром зсуву або зсувним регістром.

48