Page 24 - 4863

P. 24

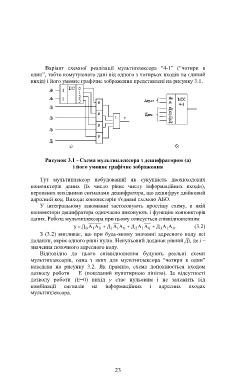

Варіант схемної реалізації мультиплексора “4-1” (“чотири в

один”, тобто комутуючого дані від одного з чотирьох входів на єдиний

вихід) і його умовне графічне зображення представлені на рисунку 3.1.

Рисунок 3.1 - Схема мультиплексора з дешифратором (а)

і його умовне графічне зображення

Тут мультиплексор побудований як сукупність двохвходових

конюнкторів даних (їх число рівне числу інформаційних входів),

керованих вихідними сигналами дешифратора, що дешифрує двійковий

адресний код. Виходи конюнкторів з'єднані схемою АБО.

У інтегральному виконанні застосовують простішу схему, в якій

конюнктори дешифратора одночасно виконують і функцію конюнкторів

даних. Робота мультиплексора при цьому описується співвідношенням

y Д 0 A 1 A Д 1 A 1 A Д 2 A 1 A Д 3 A 1 A 0 . (3.2)

0

0

0

З (3.2) випливає, що при будь-якому значенні адресного коду всі

доданки, окрім одного рівні нулю. Ненульовий доданок рівний Дi, де i –

значення поточного адресного коду.

Відповідно до цього співвідношення будують реальні схеми

мультиплексорів, одна з яких для мультиплексора “чотири в один”

наведена на рисунку 3.2. Як правило, схема доповнюється входом

дозволу роботи – Е (показаний пунктирною лінією). За відсутності

дозволу роботи (Е=0) вихід у стає нульовим і не залежить від

комбінації сигналів на інформаційних і адресних входах

мультиплексора.

23