Page 93 - 4503

P. 93

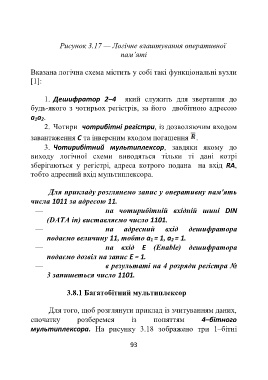

Рисунок 3.17 — Логічне влаштування оперативної

пам’яті

Вказана логічна схема містить у собі такі функціональні вузли

[1]:

1. Дешифратор 2–4 який служить для звертання до

будь-якого з чотирьох регістрів, за його двобітною адресою

a 1a 2.

2. Чотири чотрибітні регістри, із дозволяючим входом

завантаження С та інверсним входом погашення .

3. Чотирибітний мультиплексор, завдяки якому до

виходу логічної схеми виводяться тільки ті дані котрі

зберігаються у регістрі, адреса котрого подана на вхід RA,

тобто адресний вхід мультиплексора.

Для прикладу розглянемо запис у оперативну пам'ять

числа 1011 за адресою 11.

— на чотирибітній вхідній шині DIN

(DATA in) виставляємо число 1101.

— на адресний вхід дешифратора

подаємо величину 11, тобто а 1 = 1, а 2 = 1.

— на вхід Е (Enable) дешифратора

подаємо дозвіл на запис Е = 1.

— в результаті на 4 розряди регістра №

3 запишеться число 1101.

3.8.1 Багатобітний мультиплексор

Для того, щоб розглянути приклад із зчитуванням даних,

спочатку розберемся із поняттям 4–бітного

мультиплексора. На рисунку 3.18 зображено три 1–бітні

93