Page 91 - 4503

P. 91

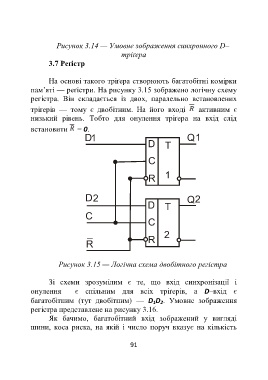

Рисунок 3.14 — Умовне зображення синхронного D–

тріґера

3.7 Реґістр

На основі такого тріґера створюють багатобітні комірки

пам’яті — реґістри. На рисунку 3.15 зображено логічну схему

регістра. Він складається із двох, паралельно встановлених

тріґерів — тому є двобітним. На його вході активним є

низький рівень. Тобто для онулення тріґера на вхід слід

встановити = 0.

Рисунок 3.15 — Логічна схема двобітного регістра

Зі схеми зрозумілим є те, що вхід синхронізації і

онулення є спільним для всіх тріґерів, а D–вхід є

багатобітним (тут двобітним) — D 1D 2. Умовне зображення

регістра представлене на рисунку 3.16.

Як бачимо, багатобітний вхід зображений у вигляді

шини, коса риска, на якій і число поруч вказує на кількість

91