Page 4 - 4503

P. 4

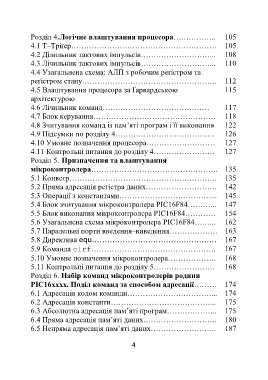

Розділ 4.Логічне влаштування процесора…………….. 105

4.1 Т–Тріґер………………………………………………… 105

4.2 Ділильник тактових імпульсів………………………... 108

4.3 Лічильник тактових імпульсів………………………... 110

4.4 Узагальнена схема: АЛП з робочим реґістром та

реґістром стану…………………………………………….. 112

4.5 Влаштування процесора за Ґарвардською 115

архітектурою

4.6 Лічильник команд…………………………………… 117

4.7 Блок керування………………………………………… 118

4.8 Зчитування команд із пам’яті програм і її виконання 122

4.9 Підсумки по розділу 4………………………………… 126

4.10 Умовне позначення процесора……………………… 127

4.11 Контрольні питання до розділу 4…………………… 127

Розділ 5. Призначення та влаштування

мікроконтролера………………………………………….. 135

5.1 Конвеєр…………………………………………………. 135

5.2 Пряма адресація регістра даних………………………. 142

5.3 Операції з константами………………………………... 145

5.4 Блок зчитування мікроконтролера PIC16F84………... 147

5.5 Блок виконання мікроконтролера PIC16F84………… 154

5.6 Узагальнена схема мікроконтролера PIC16F84……... 162

5.7 Паралельні порти введення–виведення………………. 163

5.8 Директива equ…………………………………………. 167

5.9 Команда clrf…………………………………………. 167

5.10 Умовне позначення мікроконтролера………………. 168

5.11 Контрольні питання до розділу 5…………………… 168

Розділ 6. Набір команд мікроконтролерів родини

PIC16хххх. Поділ команд за способом адресації……… 174

6.1 Адресація кодом команди……………………………... 174

6.2 Адресація константи…………………………………... 175

6.3 Абсолютна адресація пам’яті програм……………….. 175

6.4 Пряма адресація пам’яті даних……………………….. 180

6.5 Непряма адресація пам’яті даних…………………….. 187

4