Page 299 - 4503

P. 299

TMR0, адреса якого, як відомо, h’01’. При цьому відбудеться

скидання попереднього ділильника частоти.

В цілому, для керування таймером у регістрі

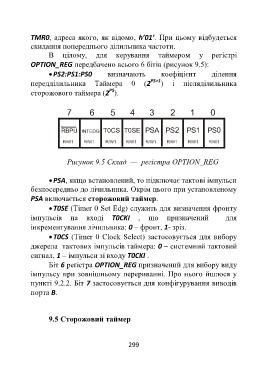

OPTION_REG передбачено всього 6 бітів (рисунок 9.5):

PS2:PS1:PS0 визначають коефіцієнт ділення

передділильника Таймера 0 (2 PS+1 ) і післяділильника

PS

сторожового таймера (2 ).

Рисунок 9.5 Склад — регістра OPTION_REG

PSA, якщо встановлений, то підключає тактові імпульси

безпосередньо до лічильника. Окрім цього при установленому

PSA включається сторожовий таймер.

T0SE (Timer 0 Set Edg) служить для визначення фронту

імпульсів на вході T0CKI , що призначений для

інкрементування лічильника: 0 – фронт, 1- зріз.

T0CS (Timer 0 Clock Select) застосовується для вибору

джерела тактових імпульсів таймера: 0 – системний тактовий

сигнал, 1 – імпульси зі входу T0CKI .

Біт 6 реґістра OPTION_REG призначений для вибору виду

імпульсу при зовнішньому перериванні. Про нього йшлося у

пункті 9.2.2. Біт 7 застосовується для конфігурування виводів

порта В.

9.5 Сторожовий таймер

299