Page 298 - 4503

P. 298

Як і більшість регістрів, TMR0 має вісім бітів, тому

його максимальним вмістом є число h’FF’, котре при

наступному вхідному такті зміниться на число h’00’. Власне

так настане переповнення таймера і буде згенерована

відповідна ознака переривання T0IF.

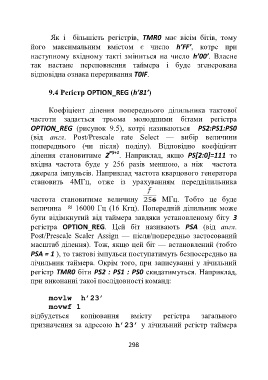

9.4 Реґістр OPTION_REG (h’81’)

Коефіціент ділення попереднього ділильника тактової

частоти задається трьома молодшими бітами регістра

OPTION_REG (рисунок 9.5), котрі називаються PS2:PS1:PS0

(від англ. Post/Prescale rate Select — вибір величини

попереднього (чи після) поділу). Відповідно коефіцієнт

ділення становитиме 2 PS+1 . Наприклад, якщо PS[2:0]=111 то

вхідна частота буде у 256 разів меншою, а ніж частота

джерела імпульсів. Наприклад частота кварцового генератора

становить 4МГц, отже із урахуванням передділильника

частота становитиме величину МГц. Тобто це буде

величина 16000 Гц (16 Кгц). Попередній ділильник може

бути відімкнутий від таймера завдяки установленому біту 3

регістра OPTION_REG. Цей біт називають PSA (від англ.

Post/Prescale Scaler Assign — після/попередньо застосований

масштаб ділення). Тож, якщо цей біт — встановлений (тобто

PSA = 1 ), то тактові імпульси поступатимуть безпосередньо на

лічильник таймера. Окрім того, при записуванні у лічильний

регістр TMR0 біти PS2 : PS1 : PS0 скидатимуться. Наприклад,

при виконанні такої послідовності команд:

movlw h’23’

movwf 1

відбудеться копіювання вмісту регістра загального

призначення за адресою h’23’ у лічильний регістр таймера

298