Page 168 - 4503

P. 168

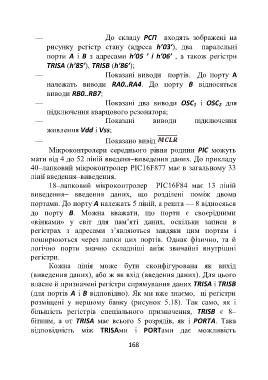

— До складу РСП входять зображені на

рисунку регістр стану (адреса h’03’), два паралельні

порти А і В з адресами h’05 ’ і h’06’ , а також регістри

TRISA (h’85’), TRISB (h’86’);

— Показані виводи портів. До порту А

належать виводи RA0..RA4. До порту В відносяться

виводи RB0..RB7;

— Показані два виводи OSC 1 і OSC 2 для

підключення кварцового резонатора;

— Показані виводи підключення

живлення Vdd і Vss;

— Показано вивід

Мікроконтролери середнього рівня родини РІС можуть

мати від 4 до 52 ліній введеня–виведення даних. До прикладу

40–лапковий мікроконтролер РІС16F877 має в загальному 33

лінії введення–виведення.

18–лапковий мікроконтролер PIC16F84 має 13 ліній

виведення– введення даних, що розділені поміж двома

портами. До порту А належать 5 ліній, а решта — 8 відносяься

до порту В. Можна вважати, що порти є своєрідними

«вінками» у світ для пам’яті даних, оскільки записи в

регістрах з адресами з’являються завдяки цим портам і

поширюються через лапки цих портів. Однак фізично, та й

логічно порти значно складніші аніж звичайні внутрішні

регістри.

Кожна лінія може бути сконфігурована як вихід

(виведення даних), або ж як вхід (введення даних). Для цього

власне й призначені регістри спрямування даних TRISA і TRISB

(для портів А і В відповідно). Як ми вже знаємо, ці реґістри

розміщені у першому банку (рисунок 5.18). Так само, як і

більшість регістрів спеціального призначення, TRISB є 8–

бітним, а от TRISA має всього 5 розрядів, як і PORTA. Така

відповідність між TRISAми і PORTами дає можливість

168