Page 101 - 4339

P. 101

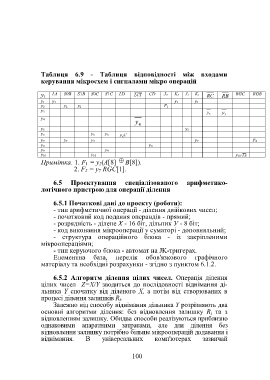

Таблиця 6.9 - Таблиця відповідності між входами

керування мікросхем і сигналами мікро операцій

LA S0B S1B S0C S1C LD CD RGC RGB

у і LCT J 2 K 2 J 1 K 1 RC RB

y 1 y 1 y 1 y 1

y 2 y 2 y 2 F 1

y 3

3 y y

3

y 4

y

4

y 5 y 5

y 6 y 6 y 6 C

y 6

y 7 y 7 y 7 y 7 F 2

y 8 y 8

y 9 y 9

y 10 y 10 y 10T2

Примітка. 1. F 1 = у 2(А[8] B[8]).

2. F 2 = y 7 RGС[1].

6.5 Проектування спеціалізованого арифметико-

логічного пристрою для операції ділення

6.5.1 Початкові дані до проекту (роботи):

- тип арифметичної операції - ділення двійкових чисел;

- початковий код подання операндів - прямий;

- розрядність - ділене X - 16 біт, дільник У - 8 біт;

- код виконання мікрооперації у суматорі - доповняльний;

- структура операційного блока - із закріпленими

мікроопераціями;

- тип керуючого блока - автомат на JK-тригерах.

Елементна база, перелік обов'язкового графічного

матеріалу та необхідні розрахунки - згідно з пунктом 6.1.2.

6.5.2 Алгоритм ділення цілих чисел. Операція ділення

цілих чисел Z=Х/Y зводиться до послідовності віднімання ді-

льника Y спочатку від діленого X, а потім від створюваних в

процесі ділення залишків R i.

Залежно від способу віднімання дільника Y розрізняють два

основні алгоритми ділення: без відновлення залишку R i та з

відновленням залишку. Обидва способи реалізуються приблизно

однаковими апаратними затратами, але для ділення без

відновлення залишку потрібно більше мікрооперацій додавання і

віднімання. В універсальних комп'ютерах зазвичай

100