Page 67 - 149

P. 67

Арифметико-логічний пристрій (АЛП) має 16-ти бітовий комбінаційний

суматор, при допомозі якого виконуються арифметичні операції, набір

комбінаційних схем для виконання логічних операцій, схеми для операцій

зсуву і десяткової корекції, а також регістри для тимчасового зберігання

операндів і результатів.

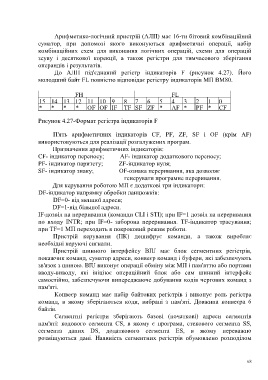

До АЛП під'єднаний регістр індикаторів F (рисунок 4.27). Його

молодший байт FL повністю відповідає регістру індикаторів МП ВМ80.

FH FL

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

* * * * ОF ОF IF TF SF ZF * АF * РF * СF

Рисунок 4.27-Формат регістра індикаторів F

П'ять арифметичних індикаторів СF, РF, ZF, SF і ОF (крім АF)

використовуються для реалізації розгалужених програм.

Призначення арифметичних індикаторів:

СF- індикатор переносу; АF- індикатор додаткового переносу;

РF- індикатор паритету; ZF-індикатор нуля;

SF- індикатор знаку; ОF-ознака переривання, яка дозволяє

генерувати програмне переривання.

Для керування роботою МП є додаткові три індикатори:

DF-індикатор напрямку обробки ланцюжків:

DF=0- від меншої адреси;

DF=1-від більшої адреси.

ІF-дозвіл на переривання (команди СLI і STI); при ІF=1 дозвіл на переривання

по входу INTR; при ІF=0- заборона переривання. ТF-індикатор трасування;

при ТF=1 МП переходить в покроковий режим роботи.

Пристрій керування (ПК) дешифрує команди, а також виробляє

необхідні керуючі сигнали.

Пристрій шинного інтерфейсу ВIU має блок сегментних регістрів,

покажчик команд, суматор адреси, конвеєр команд і буфери, які забезпечують

зв'язок з шиною. ВIU виконує операції обміну між МП і пам'яттю або портами

вводу-виводу, які ініціює операційний блок або сам шинний інтерфейс

самостійно, забезпечуючи випереджаюче добування кодів чергових команд з

пам'яті.

Конвеєр команд має набір байтових регістрів і виконує роль регістра

команд, в якому зберігаються коди, вибрані з пам'яті. Довжина конвеєра 6

байтів.

Сегментні регістри зберігають базові (початкові) адреси сегментів

пам'яті: кодового сегмента СS, в якому є програма, стeкового сегмента SS,

сегмента даних DS, додаткового сегмента ЕS, в якому переважно

розміщуються дані. Наявність сегментних регістрів обумовлено розподілом

68