Page 65 - 149

P. 65

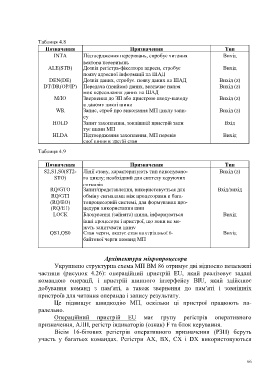

Таблиця 4.8

Позначення Призначення Тип

INTA Підтвердження переривань, спробує читання Вихід

вектора переривань

ALE(STB) Дозвіл регістра-фіксатора адреси, стробує Вихiд

появу адресної інформації на ШАД

DEN(DE) Дозвіл даних, стробує. появу даних на ШАД Вихід (z)

DT/DR(OP/IP) Передача (прийом) даних, визначає напря Вихід (z)

мок пересилання даних на ШАД

M/IO Звернення до ЗП або пристрою вводу-виводу Вихід (z)

в даному циклі шини

WR Запис, строб про виконання МП циклу запи- Вихід (z)

су

HOLD Запит захоплення, зовнішній пристрій запи Вхід

тує шини МП

HLDA Підтвердження захоплення, МП перевів Вихід

свої шини в третій стан

Таблиця 4.9

Позначення Призначення Тип

S2,S1,S0(SТ2- Лінії стану, характеризують тип виконувано- Вихід (z)

SТО) го циклу; необхідний для синтезу керуючих

сигналів

RQ/GTO Запит/представлення, використовується для Вхід/вихід

RQ/GTI обміну сигналами між процесорами в бага-

(RQ/ЕО) топроцесорній системі, для формування про-

(RQ/Е1) цедури використання шин

LOСК Блокування (зайнята) шини, інформуються Вихід

інші процесори і пристрої, що вони не мо-

жуть запитувати шину

QS1,QS0 Стан черги, вказує стан внутрішньої 6- Вихід

байтової черги команд МП

Архітектура мікропроцесора

Укрупнено структурна схема МП ВМ 86 отримує дві відносно незалежні

частини (рисунок 4.26): операційний пристрій ЕU, який реалізовує задані

командою операції, і пристрій шинного інтерфейсу ВIU, який здійснює

добування команд з памяті, а також звернення до памяті і зовнішніх

пристроїв для читання операнда і запису результату.

Це підвищує швидкодію МП, оскільки ці пристрої працюють па-

ралельно.

Операційний пристрій ЕU має групу регістрів оперативного

призначення, АЛП, регістр індикаторів (ознак) F та блок керування.

Вісім 16-бітових регістрів оперативного призначення (РЗП) беруть

участь у багатьох командах. Регістри АХ, ВХ, СХ і DХ використовуються

66