Page 186 - 149

P. 186

18С442 8192х16 USART

4 +

16384 512 40 34 10 (2), 2 + -

I²C/SPI WDT

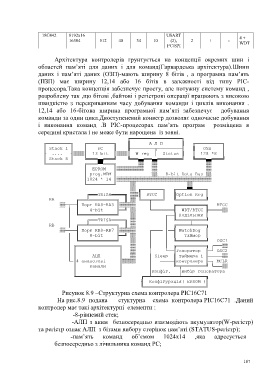

Архітектура контролерів грунтується на концепції окремих шин і

областей пам’яті для даних і для команд(Гарвардська архітектура).Шини

даних і пам’яті даних (ОЗП)-мають ширину 8 бітів , а програмна пам’ять

(ПЗП) має ширину 12,14 або 16 бітів в залежності від типу РІС-

процесора.Така концепція забезпечує просту, але потужну систему команд ,

розроблену так ,що бітові ,байтові і регістрові операції працюють з високою

швидкістю з перекриванням часу добування команди і циклів виконання .

12,14 або 16-бітова ширина програмної пам’яті забезпечує добування

команди за один цикл.Двоступеневий конвеєр дозволяє одночасне добування

і виконання команд .В РІС-процесорах пам’ять програм розміщена в

середині кристала і не може бути нарощена із зовні.

╔═══════════════════╗

╔═════════╗ ╔══════════╗ ║ А Л П ║ ╔══════════╗

║ Stack 1 ║ ║ PC ║ ╟─────────┬─────────╢ ║ ОЗП ║

╟ .... ╢▒▒▒▒║ 13 bit ║▒▒▒▒║ W reg │ Status ║ ║ 128 *8 ║

║ Stack 8 ║ ╚════▄▄════╝ ╚═══▄▄═══▄▄═════════╝ ╚════▄▄════╝

╚═════════╝ ╔════▀▀════╗ ▒▒ ▒▒ ▒▒

║ EPROM ║▒▒▒▒▒▒▒▒▒▒ ▒▒ ▒▒

║ prog.MEM ║ ▒▒ 8-bit Data Bus ▒▒

║1024 * 14 ║▒▒▒▒▒▒▒▒▒▒▒▒▒▒▒▒▒▒▒▒▒▒▒▒▒▒▒▒▒▒▒▒▒▒▒

╚══════════╝ ▒▒ ▒▒

▒▒ ╔════════╗ ╔════▀▀═════╗

╔═══TRISA═════╗ ▒▒▒║ RTCC ║ ║Option Reg ║

RA ╔═══╩══════════╗ ║ ▒▒ ╚═══╤════╝ ╚═══════════╝

▒▒─┬──╢ Порт RA0-RA3 ║▒▒▒▒▒▒ │ ╔═══════════╗ RTCC

│ ║ 4-bit ╠══╝ ▒▒ └────────╢ WDT/RTCC ╟─────▒▒

│ ╚══════════════╝ ▒▒ ┌──╢ Подільник ║

│ ╔═══TRISB═════╗ ▒▒ │ ╚═════╤═════╝

RB │ ╔═══╩══════════╗ ║ ▒▒ │ ╔═════╧═════╗

▒▒────╢ Порт RB0-RB7 ║▒▒▒▒▒▒ ┌──── │──╢ WatchDog ║

│ ║ 8-bit ╠══╝ ▒▒ │ │ ║ Tаймер ║

│ ╚══════════════╝ ▒▒ │ │ ╚═══════════╝ OSC1

│ ╔════════════════╗ ▒▒ │ │ ╔═══════════╗ ┌───▒▒

│ ║ ║ ▒▒ │ └──╢Генератор ╟─┘ OSC2

│ ║ АЦП ║ ▒▒ │ Sleep ║ таймера і ╟─────▒▒

└─║4 аналогові ║▒▒▒▒▒ │ ─────╢контролера ╟─┐ MCLR

║ канали ║ │ ╚═╤═════════╝ └───▒▒

║ ║ │Конфіг. │Вибір генератора

╚════════════════╝ ╔══╧══════════╧═════════╗

╢ Конфігурація( EPROM )║

╚═══════════════════════╝

Рисунок 8.9 –Структурна схема контролера РІС16С71

На рис.8.9 подана стуктурна схема контролера РІС16С71 .Даний

контролер має такі архітектурні елементи :

-8-рівневий стек;

-АЛП з яким безпосередньо взаємодіють акумулятор(W-регістр)

та регістр ознак АЛП з бітами вибору сторінок пам’яті (STATUS-регістр);

-пам’ять команд об’ємом 1024х14 ,яка адресується

безпосередньо з лічильника команд РС;

187