Page 33 - 4875

P. 33

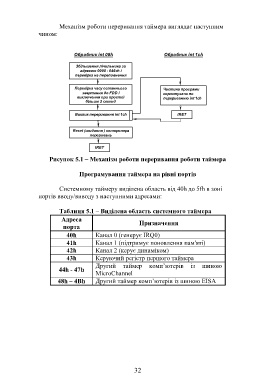

Механізм роботи переривання таймера виглядає наступним

чином:

Обробник int 08h Обробник int 1сh

Збільшення лічильника за

адресою 0000 : 046ch і

перевірка на переповнення

Перевірка часу останнього Частина програми

звертання до FDD і користувача по

виключення при простої перериванню int 1сh

більше 2 секунд

Виклик переривання int 1сh IRET

Reset (скидання ) контролера

переривань

IRET

Рисунок 5.1 – Механізм роботи переривання роботи таймера

Програмування таймера на рівні портів

Системному таймеру виділена область від 40h до 5fh в зоні

портів вводу/виводу з наступними адресами:

Таблиця 5.1 – Виділена область системного таймера

Адреса

Призначення

порта

40h Канал 0 (генерує IRQ0)

41h Канал 1 (підтримує поновлення пам'яті)

42h Канал 2 (керує динаміком)

43h Керуючий регістр першого таймера

Другий таймер комп’ютерів із шиною

44h - 47h

MicroChannel

48h – 4Вh Другий таймер комп’ютерів із шиною EISA

32