Page 18 - 4874

P. 18

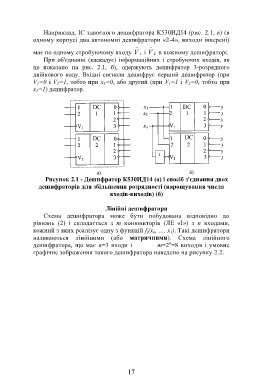

Наприклад, ІС здвоєного дешифратора К530ИД14 (рис. 2.1, а) (в

одному корпусі два автономні дешифратори «2-4», виходи інверсні)

має по одному стробуючому входу V і V в кожному дешифраторі.

2

1

При об'єднанні (каскадує) інформаційних і стробуючих входів, як

це показано на рис. 2.1, б), одержують дешифратор 3-розрядного

двійкового коду. Вхідні сигнали дешифрує перший дешифратор (при

V 1=0 і V 2=1, тобто при х 3=0, або другий (при V 1=1 і V 2=0, тобто при

х 3=1) дешифратор.

Рисунок 2.1 - Дешифратор К530ИД14 (а) і спосіб з'єднання двох

дешифраторів для збільшення розрядності (нарощування числа

входів-виходів) (б)

Лінійні дешифратори

Схема дешифратора може бути побудована відповідно до

рівнянь (2) і складається з m конюнкторів (ЛЕ «І») з n входами,

кожний з яких реалізує одну з функцій f j(x n, ..., x 1). Такі дешифратори

називаються лінійними (або матричними). Схема лінійного

n

дешифратора, що має n=3 входи і m=2 =8 виходів і умовне

графічне зображення такого дешифратора наведено на рисунку 2.2.

17