Page 40 - 4863

P. 40

прийнято прямий вихід позначати –Q , а інверсний –Q . Стани тригера

визначають за рівнем напруги на його прямому виході. Якщо це

напруга рівня логічної одиниці, то говорять, що тригер перебуває в

одиничному стані (в тригер записана “1”). Якщо ж тригер знаходиться

в нульовому стані (записаний “0”).

За логічним функціонуванням розрізняють тригери типів RS, D,

T, JK. Крім того, використовують комбіновані тригери, в яких

поєднуються одночасно декілька типів, і тригери, зі складною вхідною

логікою (групами входів, зв'язаних між собою логічними

залежностями).

Найпростіший тригер має тільки один інформаційний вхід (Т),

зберігає свій стан при подачі на нього сигналу рівня “0” і змінює стан

на протилежне при подачі вхідного сигналу рівня “1”. Такий тригер

називається рахунковим (з рахунковим входом) або Т-

тригером(«toggle»-перемикач, тумблер), його умовне графічне

зображення наведено на рисунку 5.2. З таблиці переходів цього тригера

(табл. 5.1) одержимо вираз для характеристичного рівняння

k k k

k

k1

Q Q T Q T (5.4)

k1 k k k k

Q Q T Q T

Неважко побачити, що Т-тригер реалізує логічну функцію “сума за

модулем 2”.

D-тригер («delay»-затримка, рис. 5.2) також має один

інформаційний вхід (D). Його стан повторює вхідний сигнал

попереднього такту. Переходи D-тригера представлені в табл. 5.2.

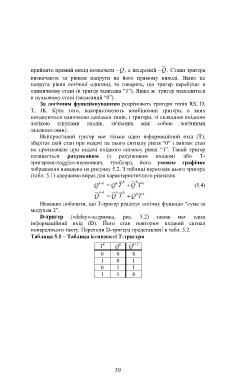

Таблиця 5.1 – Таблиця істинності Т-тригера

k

k

T Q Q k+1

0 0 0

1 0 1

0 1 1

1 1 0

39