Page 156 - 4859

P. 156

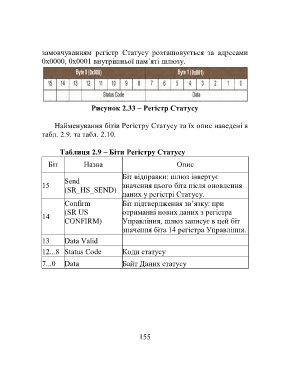

замовчуванням регістр Статусу розташовується за адресами

0x0000, 0x0001 внутрішньої пам’яті шлюзу.

Рисунок 2.33 – Регістр Статусу

Найменування бітів Регістру Статусу та їх опис наведені в

табл. 2.9. та табл. 2.10.

Таблиця 2.9 – Біти Регістру Статусу

Біт Назва Опис

Біт відправки: шлюз інвертує

Send

15 значення цього біта після оновлення

(SR_HS_SEND)

даних у регістрі Статусу.

Confirm Біт підтвердження зв’язку: при

(SR US отриманні нових даних з регістра

14

CONFIRM) Управління, шлюз записує в цей біт

значення біта 14 регістра Управління.

13 Data Valid

12...8 Status Code Коди статусу

7...0 Data Байт Даних статусу

155