Page 84 - 4503

P. 84

3.3 Синхронізація цифрових вузлів

Розрив у часі між тактами, тобто між логічними

одиницями є гарантовано більшим ніж t затр. А раз так, то

використовуючи у логічній схемі розгалужену магістраль для

поширення тактових імпульсів, можна гарантувати

синхронність її роботи. Для ілюстрації синхронізації

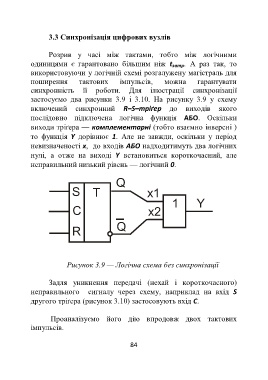

застосуємо два рисунки 3.9 і 3.10. На рисунку 3.9 у схему

включений синхронний R–S–тріґер до виходів якого

послідовно підключена логічна функція АБО. Оскільки

виходи тріґера — комплементарні (тобто взаємно інверсні )

то функція Y дорівнює 1. Але не завжди, оскільки у період

невизначеності х, до входів АБО надходитимуть два логічних

нулі, а отже на виході Y встановиться короткочасний, але

неправильний низький рівень — логічний 0.

Рисунок 3.9 — Логічна схема без синхронізації

Задля уникнення передачі (нехай і короткочасного)

неправильного сигналу через схему, наприклад на вхід S

другого тріґера (рисунок 3.10) застосовують вхід С.

Проаналізуємо його дію впродовж двох тактових

імпульсів.

84