Page 184 - 4503

P. 184

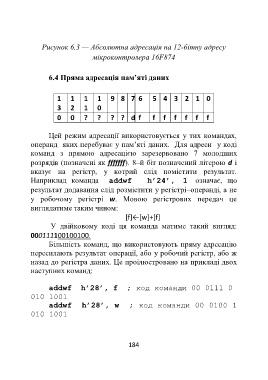

Рисунок 6.3 — Абсолютна адресація на 12-бітну адресу

мікроконтролера 16F874

6.4 Пряма адресація пам’яті даних

1 1 1 1 9 8 7 6 5 4 3 2 1 0

3 2 1 0

0 0 ? ? ? ? d f f f f f f f

Цей режим адресації використовується у тих командах,

операнд яких перебуває у пам’яті даних. Для адреси у коді

команд з прямою адресацією зарезервовано 7 молодших

розрядів (позначені як fffffff). 8–й біт позначений літерою d і

вказує на регістр, у котрий слід помістити результат.

Наприклад команда addwf h’24’, 1 означає, що

результат додавання слід розмістити у регістрі–операнді, а не

у робочому регістрі w. Мовою регістрових передач це

виглядатиме таким чином:

[f]←[w]+[f]

У двійковому коді ця команда матиме такий вигляд:

000111100100100.

Більшість команд, що використовують пряму адресацію

пересилають результат операції, або у робочий регістр, або ж

назад до регістра даних. Це проілюстровано на прикладі двох

наступних команд:

addwf h’28’, f ; код команди 00 0111 0

010 1001

addwf h’28’, w ; код команди 00 0100 1

010 1001

184