Page 108 - 4503

P. 108

4 Узагальнена схема: АЛП разом із робочим регістром

та регістром стану

5 Влаштування процесора за гарвардською

архітектурою

6 Лічильник команд

7 Блок керування

8 Зчитування команди з пам’яті програм і її

виконання

У цій лекції йтиметься про логічне влаштування

процесора і дотепер не розглянуті функціональні вузли

цифрової автоматики, без котрих складно пояснити

функціонування процесора. Це насамперед лічильники і вузли

на їх основі. Розповідь про лічильники буде більш вдалою,

якщо розпочати зі знайомства з так званим тактовим трігером,

тобто Т–тріґером.

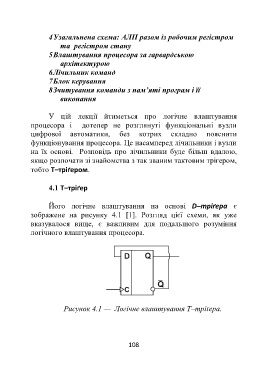

4.1 Т–тріґер

Його логічне влаштування на основі D–тріґера є

зображене на рисунку 4.1 [1]. Розгляд цієї схеми, як уже

вказувалося вище, є важливим для подальшого розуміння

логічного влаштування процесора.

Рисунок 4.1 — Логічне влаштування Т–тріґера.

108