Page 156 - 149

P. 156

Порти вводу/виводу інформації

Всі чотири порти МК51 використовуються для вводу або виводу

інформації побайтно, утворюючи 32-розрядну шину вводу-виводу. Кожний

порт має керований регістр-фіксатор, вхідний буфер і вихідний драйвер.

Фіксатор є 8-розрядним регістром з байтовою і бітовою адресацією для

встановлення розрядів програмним шляхом. У ньому фіксуються тільки

вихідні дані, але не фіксуються вхідні.

Вихідні драйвери портів 0 і 2, а також вхідний буфер порту 0 беруть

участь при зверненні до зовнішньої пам’яті (ЗП). При цьому через порт 0 в

режимі часового розділення спочатку виводиться молодший байт адреси

комірки ЗП, а потім видається або приймається байт даних. Через порт 2

виводиться старший байт адреси в тих випадках, коли розрядність адреси

рівна 16 бітам. Очевидно, що в цьому випадку дані порти не можуть бути

використані для подовження шини вводу-виводу.

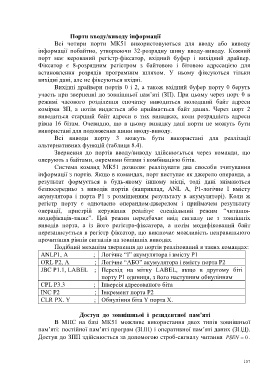

Всі виводи порту 3 можуть бути використані для реалізації

альтернативних функцій (таблиця 8.4).

Звернення до портів вводу/виводу здійснюєьться через команди, що

оперують з байтами, окремими бітами і комбінацією бітів.

Система команд МК51 дозволяє реалізувати два способи зчитування

інформації з портів. Якщо в командах, порт виступає як джерело операнда, а

результат формується в будь-якому іншому місці, тоді дані знімаються

безпосередньо з виводів портів (наприклад, ANL A, P1-логічне І вмісту

акумулятора і порта Р1 з розміщенням результату в акумуляторі). Коли ж

регістр порту є одночасно операндом-джерелом і приймачем результату

операції, пристрій керування реалізує спеціальний режим “читання-

модифікація-запис”. Цей режим передбачає ввід сигналу не з зовнішніх

виводів порта, а із його регістра-фіксатора, а потім модифікований байт

перезаписується в регістр фіксатор, що виключає можливість неправильного

прочитання рівнів сигналів на зовнішніх виводах.

Подібний механізм звернення до портів реалізований в таких командах:

ANLP1, A ; Логічне “І” акумулятора і вмісту Р1

ORL P2, A ; Логічне “АБО” акумулятора і вмісту порта Р2

JBC P1.1, LABEL ; Перехід на мітку LABEL, якщо в другому біті

порту Р1 одиниця, з його наступним обнулінням

CPL P3.3 ; Інверсія адресованого біта

INC P2 ; Інкремент порта Р2

CLR PX. Y ; Обнуління біта Y порта X.

Доступ до зовнішньої і резидентної пам’яті

В МПС на базі МК51 можливе використання двох типів зовнішньої

пам’яті: постійної пам’яті програм (ЗПП) і оперативної пам’яті даних (ЗПД).

Доступ до ЗПП здійснюється за допомогою строб-сигналу читання PSEN 0 .

157