Page 148 - 149

P. 148

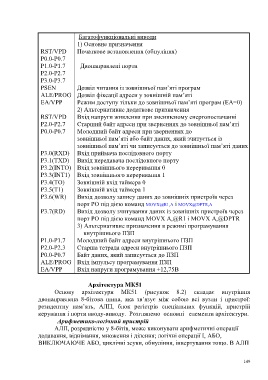

Багатофункціональні виводи

1) Основне призначення

RST/VPD Початкове встановлення (обнуління)

P0.0-P0.7

P1.0-P1.7 Двонаправлені порти

P2.0-P2.7

P3.0-P3.7

PSEN Дозвіл читання із зовнішньої пам’яті програм

ALE/PROG Дозвіл фіксації адреси у зовнішній пам’яті

EA/VPP Режим доступу тільки до зовнішньої пам’яті програм (ЕА=0)

2) Альтернативне додаткове призначення

RST/VPD Вхід напруги живлення при зменшеному енергопостачанні

P2.0-P2.7 Старший байт адреси при зверненнях до зовнішньої пам’яті

P0.0-P0.7 Молодший байт адреси при зверненнях до

зовнішньої пам’яті або байт даних, який зчитується із

зовнішньої пам’яті чи записується до зовнішньої пам’яті даних

P3.0(RXD) Вхід приймача послідовного порту

P3.1(TXD) Вихід передавача послідовного порту

P3.2(INTO) Вхід зовнішнього переривання 0

P3.3(INT1) Вхід зовнішнього переривання 1

P3.4(TO) Зовнішній вхід таймера 0

P3.5(T1) Зовнішній вхід таймера 1

P3.6(WR) Вихід дозволу запису даних до зовнішніх пристроїв через

порт РО під дією команд MOVX@R1,A i MOVX@DPTR,A

P3.7(RD) Вихід дозволу зчитування даних із зовнішніх пристроїв через

порт РО під дією команд MOVX A,@R1 i MOVX A,@DPTR

3) Альтернативне призначення в режимі програмування

внутрішнього ПЗП

P1.0-P1.7 Молодший байт адреси внутрішнього ПЗП

P2.0-P2.3 Старша тетрада адреси внутрішнього ПЗП

P0.0-P0.7 Байт даних, який записується до ПЗП

ALE/PROG Вхід імпульсу програмування ПЗП

EA/VPP Вхід напруги програмування +12,75В

Архітектура МК51

Основу архітектури МК51 (рисунок 8.2) складає внутрішня

двонаправлена 8-бітова шина, яка зв’язує між собою всі вузли і пристрої:

резидентну пам’ять, АЛП, блок регістрів спеціальних функцій, пристрій

керування і порти вводу-виводу. Розглянемо основні елементи архітектури.

Арифметико-логічний пристрій

АЛП, розрядністю у 8-бітів, може виконувати арифметичні операції

додавання, віднімання, множення і ділення; логічні операції І, АБО,

ВИКЛЮЧАЮЧЕ АБО, циклічні зсуви, обнуління, інвертування тощо. В АЛП

149